本文共 6382 字,大约阅读时间需要 21 分钟。

GTX模块

Virtex-6支持多种高速串行接口,其中高速串行模块GTX收发器可以实现150Mbit/s~6.5Gbit/s的线速率。GTX收发器是芯片与芯片之间、板与板之间进行串行通信的首选解决方案。GTX收发器具有以下特性。

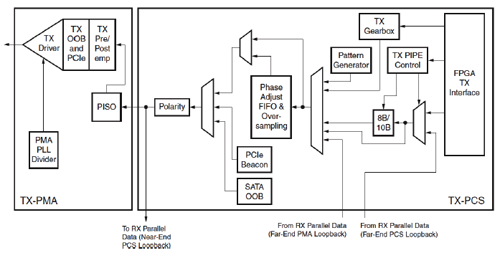

灵活的SERDES支持多速率应用。功能强大的发射预加重和接收均衡功能,具有最佳的信号完整性。集成式“变速箱”可以实现灵活编码:8B/10B、64B/66B、64B/67B。高度灵活的时钟控制,接收与发送独立。可以与片上PCI Express和三态以太网MAC模块连接。相比以前的产品,收发器功耗降低了25%,在6.5Gbit/s下,功率低于150mW(典型值)。符合常用标准,如10/40/100G以太网、PCI Express、OC-48、XAUI、SRIO和HD-SDI。 Virtex-6器件中包含12~36个GTX收发器模块,GTX发射与接收模块框图如图5-37所示。GTX收发器包含物理编码子层(PCS)和物理媒体接入子层(PMA)。PMA包含串行/解串器(SERDES)、TX和RX输入/输出缓冲、时钟产生器和时钟恢复电路。PCS包含8B/10B编码/解码器、弹性缓冲器。

发送的并行数据经过8B/10B编码后,写入发送端FIFO,然后转换成串行差分数据发送出去。接收端接收到的串行差分信号首先经过接收端缓冲,然后经过串并转化器转换成并行数据,再经过8B/10B解码,写入弹性缓冲,最后并行输出。

PCS具有8B/10B编码器/解码器。MGT可以工作在32位或40位操作模式,可以在配置或者运行过程中更改PMA速率和PCS协议,可以根据时钟来配置内部数据宽度和外部数据宽度。

PMA提供与外部媒体的模拟接口,其中包括:20倍时钟倍频器、发送端时钟生成器、发送缓冲器、串行器、接收端的时钟恢复电路、接收缓冲器、解串器、可变速率的全双工收发器、可编程的五级差分输出幅度(摆率)控制和可编程的四级输出预加重模块等。

MGT中的几个重要模块说明如下。

(1) 8B/10B编解码器。

8B/10B编码机制是由IBM公司开发的,已经被广泛采用。它是一种数值查找类型的编码机制,可将8位的字符转化为10位字符。转化后的字符可以保证有足够的跳变用于时钟恢复。8B/10B编码具有“0”和“1”出现的概率相等,直流基线漂移小,低频分量小,功率谱带宽较窄,抖动小,以及能够检测输入数据中的错误等许多优点。

8B/10B编码可以分为256个数据字符和12个控制字符。数据字符标识为D,用于传输数据;控制字符标识为K,用于传输控制序列。12个控制字符用于对齐、控制,以及将带宽划分为子通道。

(2) comma字符检测和对齐。

Virtex-6 RrocketIO有可编程的逗号检测,以便于实现10位字符的各种通信协议和检测,通过对MCOMMA_10B_VALUE、DEC_MCOMMA_DETECT、PCOMMA_10B_VALUE、DEC_PCOMMA_DETECT和COMMA_10B_MASK这些参数的设置,可以实现任意的8位或10位符号检测。

接收器在输入数据流中扫描搜寻comma字符。如果找到,解串器就调整序列边界以匹配检测到的comma字符序列,且扫描是连续进行的。一旦对齐确定,所有后续comma字符的对齐均已确定。在任意的序列组合里,comma字符序列必须是唯一的。常用的K字符是12个K字符中的一个或多个。由于K28.1、K28.5、K28.7这些字符的头7位都是1100000,这种比特序列模式只可以在这些控制字符中出现,因此,这些控制字符是非常理想的对齐序列。

(3) 时钟修正。

在时钟/数据恢复电路的作用下,从接收的串行数据流中解出时钟的频率和相位,一般将它的20分频时钟作为恢复时钟。在恢复时钟作用下从串行数据经过解串器产生并行数据作为8B/10B译码的输入,译码后的数据进入16×52位的接收缓冲器。输入缓冲器的输入数据速率是由PCS RXCLK的频率决定的,而从缓冲器读取端输出的数据速率是由RXUSRCLK的频率决定的。由于两个时钟会有差异,所以需要进行时钟修正。

时钟修正的基本原理是:在发送端,当数据发送了一定的字节或数个数据包后,通过插入和发送一些特定的字节修正字符;在接收端,当接收到这些字符后会自动地丢弃或者重复来补偿时钟的差异。时钟修正的核心工作是在比特流中搜寻特定的字符序列。

GTH模块

Vrtex-6 HXT器件内的GTH模块比GTX有更高的线速率,用它可以实现最高性能的高速串行收发器。GTH具有如下特性。

灵活的SERDES 支持多速率应用。实现40G 和100G 协议等。功能强大的发射预加重和接收均衡器。集成式“变速箱”实现了灵活编码:8B/10B、64B/66B。低功耗:~220mW(典型值)@10.3125Gbit/s。符合常见标准的要求,如10/40/100G 以太网、PCI Express、OC-48、XAUI、SRIO 和HD-SDI。5.1.9 以太网(Ethernet MAC)模块

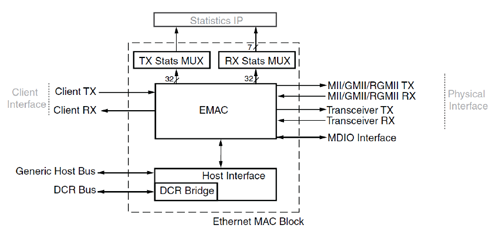

Virtex-6器件内置以太网MAC,不需要消耗可编程逻辑资源即可提供无缝的芯片到芯片连接。以太网媒体访问控制器(MAC)内核支持10/100/1000Mbit/s数据速率,兼容UNH验证标准并且具有互操作能力,设计符合IEEE 802.3规范的要求,可以单独运行在1000Mbit/s、100Mbit/s 和10Mbit/s 模式,或者配置成三态模式。支持IEEE标准的MII、GMII和RGMII协议,减少外部物理接口的总线宽度。

图5-38 所示为以太网MAC 的结构框图。

主机可以通过主机总线或者设备控制寄存器(DCR)总线与以太网MAC 互联。

物理接口能配置成MII、GMII、RGMII、SGMII 或100BASE-X,但是根据所选择的物理接口配置,只有一套TX和RX接口被激活。

EMAC有一个可选的管理数据输入/输出接口(MDIO),可以访问外部PHY 的管理寄存器和EMAC内部的物理接口管理寄存器(仅在1000BASE-X 或SGMII 模式配置下有效)。

EMAC输出统计向量包含了以太网发送和接受数据通路上的帧信息。复用统计向量以减少与外界连接时所需要的引脚数。在FPGA中实现统计IP(Statistics IP)以累计以太网MAC收发数据通路的统计信息。

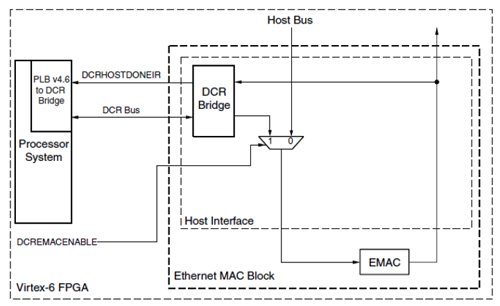

Virtex-6的EMAC的功能框图如图5-39所示。

EMAC接口路径上有个接收地址滤波器,它控制接受或拒绝输入帧。

输出统计向量包含了以太网发送和接受数据通路上的帧统计信息。发送统计向量TX_STATISTICS_VECTOR包含发送帧的统计信息,由32位向量和内部信号组成。接受统计向量RX_STATISTICS_VECTOR包含接受帧的统计信息,由28位向量和内部信号组成。Xilinx CORE Generator软件免费提供了一个外部统计模块,该统计模块对以太网MAC的发送和接收数据通路上的所有统计信息进行累加。

主机/DCR总线接口。通过主机接口可以访问EMAC配置寄存器、EMAC地址滤波寄存器、PCS/PMA子层寄存器,还可以驱动MDIO接口控制外部设备。可以通过通用主机总线或者DCR总线(当与处理器连接时)对EMAC主机接口进行访问。图5-41所示为主机接口内部结构图。Xilinx XPS工具提供了XPS_LL_TEMAC软核通过PLB总线控制EMAC。PLB和DCR总线之间可以通过桥切换。

设计中可以调用以太网MAC 的原语或者使用CoreGen 工具配置EMAC 参数来使用EMAC 模块。

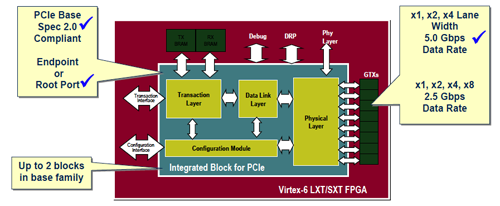

5.1.10 PCIe 端点模块

PCIe2.0 标准对满足高性能、低功耗应用的需求非常关键,特别是在电信、服务器、高端视频市场。针对越来越多的PCIe 的应用,Virtex-6 FPGA 中嵌入了第二代的PCIe 内核,该集成的第二代PCIe 模块兼容PCI Express 2.0 标准,已经通过了1-8 通道配置的PCI-SIGPCI Express 2.0 版本兼容性与互操作性测试。

Vrtex-6 FPGA 内的PCI Express 模块实现了事务处理层、数据链路层和物理层功能,能够以最低的FPGA 逻辑利用率提供完整的PCI Express 端点和根端口功能。内部结构如图5-41 所示。

5.2 Virtex-6 LXT 型FPGA

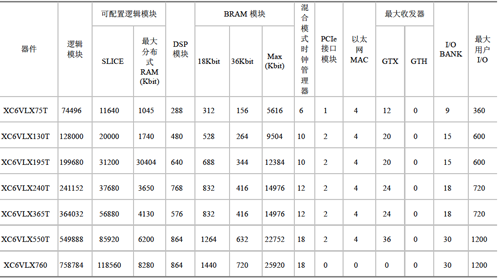

Vitex-6 LXT 平台FPGA 的Virtex-6 LXT FPGA 针对逻辑优化,同时提供6.5Gbit/s GTX收发器、内置式PCIe 和三态以太网MAC。表5-15 为Virtex-6 LXT 器件列表。

5.3 Virtex-6 SXT型FPGA

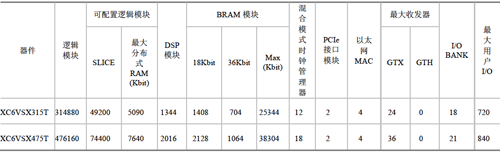

Virtex-6 SXT面向DSP优化,DSP48E1 SLICE能实现超过 1000 GMACS的性能,可以高效地完成复杂的数字信号处理,同时提供 6.5Gbit/s GTX 收发器、内置式 PCIe 和三态以太网MAC。表5-16所示为Virtex-6 SXT器件列表。

5.4 Virtex-6 HXT型FPGA

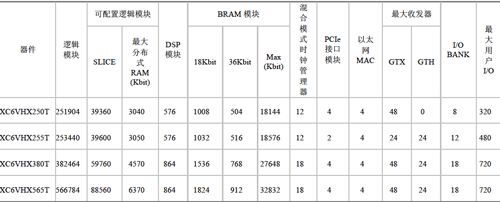

Virtex-6 HXT FPGA 针对那些需要超高速串行连接功能的应用进行了优化,通过 6.5Gbit/s GTX收发器和支持11Gbit/s以上的线路速率的GTH收发器提供了业内最高的串行带宽,从而实现了新一代分组和传输、交换机结构、视频开关和成像设备。表5-17所示为Virtex-6 HXT器件列表。

Virtex-6 HXT器件的主要特性介绍如下。

(1) 实现了最高的串行带宽。

带宽最高的FPGA提供了低风险方法,能够迅速为面向网络、电信和成像行业中的桥接、转换与群集的、功能强大的40Gbit/s和100Gbit/s应用进行原型开发和生产。面向100GE MAC和100GE-Interlaken桥接的单FPGA解决方案。面向40Gbit/s发射机应答器/复用转发器的单FPGA解决方案。利用FEC有效实现100Gbit/s发射机应答器/复用转发器。实现高级功能集成,如分组处理、加密和流量管理。GTH多速率收发器多达24个,支持11Gbit/s以上的线路速率,用于连至×10Gbit/s、40Gbit/s和100Gbit/s网络。GTX多速率收发器多达48个,支持高达6.5Gbit/s的线路速率,实现了到早期ASIC、ASSP和背板的可靠接口。(2) 新型GTH收发器支持11Gbit/s以上的线速率。

利用支持9.953Gbit/s~11.18Gbit/s线路速率的收发器构建高效的,到×10Gbit/s、40Gbit/s和100Gbit/s以太网网络的链路。单个Virtex-6 HXT FPGA内的GTH收发器多达24个。低功耗:220mW(典型值),在10.3125Gbit/s时。利用内置式Tx预加重、Rx线性均衡和Rx DFE实现芯片—芯片、芯片—光纤和10Gbit/s背板应用所需的信号完整性。用于实现简便易用性的复杂自适应均衡引擎。保证符合常见标准的要求,如10/40/100Gbit/s以太网、OTU-/2/4、OC-192和SFP+。集成式64B/66B和8B/10B编码支持。简单而高度灵活的时钟控制结构,实现了多协议设计。(3) 利用6.5Gbit/s GTX收发器实现低功耗串行连接功能。

利用支持150Mbit/s~6.5Gbit/s线路速率的收发器连至早期ASIC、ASSP和背板。功耗降低了25%:在6.5Gbit/s下,功率低于150mW(典型值)。单个Virtex-6 HXT FPGA内的GTX收发器多达48个。高度灵活的时钟控制技术实现了独立Rx和Tx操作,能够有效地将某些应用的收发器数量加倍。保证符合常见标准的要求,如10/40/100Gbit/s以太网、PCI Express、OC-48、XAUI、SRIO和HD-SDI。第二代集成式PCI Express模块和第三代三态以太网MAC模块可以轻松实现常见接口。5.5 小结

Virtex-6 FPGA是基于Virtex-5结构的,采用了第三代的ASMBL架构,比前一代产品功耗降低达50%,成本降低达20%。本章详细介绍了Virtex-6系列器件的内部各模块及其架构,以期读者对Virtex-6系列FPGA有一个较深入的认识,并在此基础上,提高设计者的设计优化能力。

转载地址:http://gacaf.baihongyu.com/